# A High Frequency Divider in 0.18 um SiGe BiCMOS Technology

Noorfazila Kamal<sup>1</sup>, Yingbo Zhu<sup>1</sup>, Leonard T. Hall<sup>1</sup>, Said F. Al-Sarawi<sup>1</sup>, Craig Burnet<sup>2</sup>, Ian Holland<sup>2</sup>, Adnan Khan<sup>2</sup>, Andre Pollok<sup>2</sup>, Justin Poyner<sup>2</sup>, Micheal Boers<sup>3</sup>, James A. Howarth<sup>3</sup>, Adam Lauterbach<sup>3</sup>, Jeffrey Harrison<sup>3</sup>, James Rathmell<sup>4</sup>, Michael Batty<sup>3</sup>, Anthony Parker<sup>3</sup>, Linda M. Davis<sup>3</sup>, William G. Cowley<sup>2</sup>, Neil H.E. Weste<sup>1,2</sup>, and Derek Abbott<sup>1</sup>

<sup>1</sup>The School of Electrical & Electronic Engineering, University of Adelaide, Adelaide, SA 5005, Australia.;

<sup>2</sup>Institute for Telecommunications Research, SPRI Building, University of South Australia, Mawson Lakes Boulevard, Mawson Lakes, SA 5095, Australia.;

<sup>3</sup>Electronics Department, Macquarie University, NSW 2109, Australia.;

<sup>4</sup>Electrical Engineering, The University of Sydney, NSW 2006, Australia.;

#### **ABSTRACT**

High speed frequency dividers are critical parts of frequency synthesisers in wireless systems. These dividers allow the output frequency from a voltage controlled oscillator to be compared with a much lower external reference frequency that is commonly used in these synthesisers. Common trade-offs in high frequency dividers are speed of division, power consumption, real estate area, and output signal dynamic range. In this paper we demonstrate the design of a high frequency, low power divider in 0.18  $\mu$ m SiGe BiCMOS technology. Three dividers are presented, which are a regenerative divider, a master-slave divider, and a combination of regenerative and master-slave dividers to perform a divide-by-8 chain. The dividers are used as part of a 60 GHz frequency synthesizer. The simulation results are in agreement with measured performance of the regenerative divider. At 48 GHz the divider consumes 18 mW from a 1.8 V supply voltage. The master-slave divider operates up to 36 GHz from a very low supply voltage, 1.8 V. The divide-by-8 operates successfully from 40 GHz to 50 GHz.

Keywords: regenerative divider, mixer, master-slave, emitter-coupled logic, 60 GHz, frequency synthesizer

#### 1. INTRODUCTION

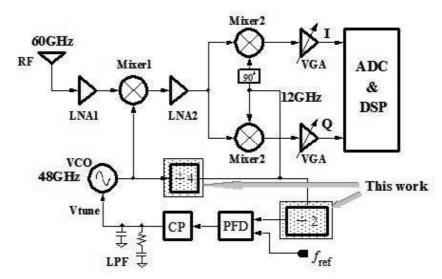

Recently, the 60 GHz band has emerged as a frequency region of great interest in RF wireless communication. This high frequency band presents a considerable challenge in the design of RF transceivers including the frequency synthesizer. A phase-locked loop is commonly used building block for a frequency synthesizer. The phase-locked loop locks the high frequency output from a voltage-controlled oscillator (VCO) to a much lower frequency reference clock. In order to compare the two signals, a high speed frequency divider is required to decrease the VCO output frequency. The frequency dividers are a part of a frequency synthesizer for a 60 GHz RF receiver. The double-conversion receiver architecture is shown in Figure 1. Two local oscillators (LO) at 48 GHz and 12 GHz are used. The first LO is the output of a voltage-controlled oscillator (VCO), while the second LO is a quarter of the first LO. The second LO is obtained by dividing the first LO, utilizing two frequency dividers. The first divider is required to handle a 48 GHz signal from the VCO. This very high frequency signal could not be handled by static master-slave divider architecture. Hence, a dynamic divider is used. This regenerative dynamic divider is utilized to divide-by-2 the VCO signal, yielding 24 GHz from 48 GHz. The 24 GHz output from the regenerative divider is divided-by-2, utilizing a master-slave divider to obtain a 12 GHz signal. The 12 GHz signal, which is the second LO is fed to the mixers to downconvert the IF signal to baseband. Another master-slave divider is used after the second LO to produce a total of 8 divisions. A few more frequency dividers might be required before the signal goes to a phase frequency detector (PFD). However, only high frequency dividers are of concern in this paper.

Three frequency divider circuits are implemented, a regenerative divider, a master-slave divider, and a divideby-8 chain. Section 2 details the circuit design. These circuits were fabricated in 0.18  $\mu$ m SiGe BiCMOS technology with  $f_t = 155$  GHz. The regenerative divider operates up to 50 GHz and consumes only 18 mW at 1.8 V supply voltage. The master-slave divider operates from a supply voltage as low as 1.8 V. Section 3 provides experimental results.

Figure 1. A 60 GHz receiver using a double-conversion architecture. By utilizing the 48 GHz first LO, a 60 GHz RF signal is translated to a 12 GHz IF. Then, the 12 GHz second LO converts the IF to baseband (ADC & DSP). The first LO is generated by a VCO, while the second LO is obtained after dividing the first LO by 4. The second LO provides a quadrature output. A PLL is used for the frequency synthesizer. Frequency dividers divide the VCO output before a phase frequency detector (PFD) compares the signal to a reference. Then a charge pump (CP) and a low pass filter (LPF) translate the errors into a voltage ( $V_{tune}$ ) to control the VCO.

# 2. CIRCUIT IMPLEMENTATION

# 2.1. Regenerative Frequency Divider

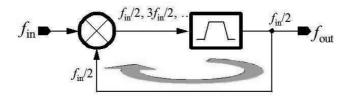

The basic concept of a regenerative divider is to produce oscillation at half of the input frequency with the aid of a feedback network. The regenerative divider consists of a mixer and a loop filter as shown in Figure 2. The input signal at frequency  $f_{\rm in}$  is mixed with the output signal at frequency  $f_{\rm in}/2$ . The mixer generates the output at  $f_{\rm in}/2$  and also contains odd harmonics  $3f_{\rm in}/2$ ,  $5f_{\rm in}/2$  etc. These harmonics are filtered out by a band-pass filter. Thus, only  $f_{\rm in}/2$  is feed back to the mixer, second input. To obtain a stable half-frequency, the loop gain must be greater than unity<sup>1,2</sup> and the total loop phase must be within  $\pm \pi/2$ . In addition, to ensure no spurious oscillation, the loop gain must be smaller than one when the input signal is absent.<sup>3</sup>

Figure 2. Regenerative frequency divider. The mixer generates the output at  $f_{\rm in}/2$ ,  $3f_{\rm in}/2$  etc. A band pass filter filtered the mixer output to obtain a signal at  $f_{\rm in}/2$ .

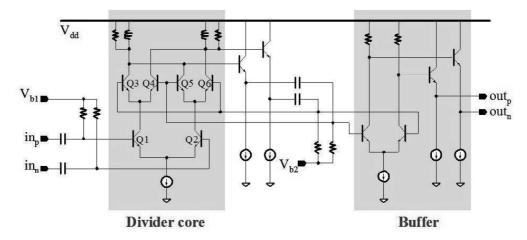

An important part of the regenerative divider is the mixer. A Gilbert mixer is used with parallel load resistors and inductors as shown in Figure 3. The input signals applied to transistors Q1 and Q2 are amplified during

the mixing operation. The output is fed back to the top transistors (Q3, Q4, Q5 and Q6). This circuit does not include the band-pass filter because the divider output is maximum at half of the operating frequency.

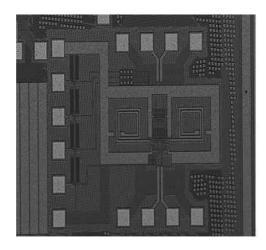

Figure 4 shows the die micrograph of the fabricated regenerative divider. The circuit consumes  $0.7~\mathrm{mm} \times 0.6~\mathrm{mm}$  in area, including pads.

${\bf Figure~3.}~{\rm Regenerative~divider~schematic}.$

Figure 4. Die micrograph of the regenerative divider in 0.18  $\mu m$  SiGe BiCMOS technology. The circuit area is 0.7  $\times$  0.6 mm<sup>2</sup>.

### 2.2. Master-Slave Frequency Divider

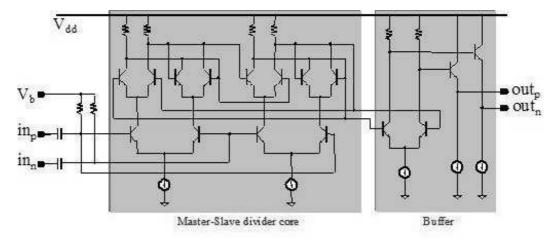

The master-slave frequency divider circuit is implemented using a conventional emitter-coupled logic (ECL) D flip-flop, as shown in Figure 5. The divider output is buffered before being used to drive other circuits. The output buffer consists of a pair of emitter followers and a differential amplifier. This circuit operates from a 1.8 V supply voltage.

The D flip-flop consists of two D latches. The output of first D latch must be able to drive the input of second D latch. Normally, emitter follower circuits are added between the D latches to provide voltage level shifting to drive the next stage.<sup>4,5</sup> However, with 1.8 V supply voltage, a voltage level shifter becomes complicated. The

proposed circuit design eliminates the emitter follower between the D latches. This was achieved by careful circuit design to enable the output level of the first D latch to drive second latch at appropriate level.

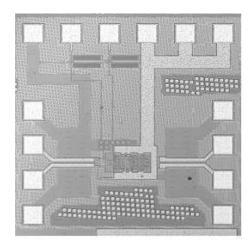

The layout is designed to be symmetrical to ensure the same delay for the differential signal. The track from input to output was designed to be as short as possible to reduce the propagation delay. The circuit consumes  $0.6 \text{ mm} \times 0.6 \text{ mm}$  area including the pads. Figure 6 shows the micrograph of the master-slave divider.

**Figure 5.** Master-slave divider schematic. The divider consists of two D latches. The output of the first latch is enabled to drive the second input latch. Hence, no voltage level shifter is required between the two latches.

Figure 6. Die micrograph of the master-slave divider in 0.18  $\mu m$  SiGe BiCMOS technology. The circuit area is 0.6  $\times$  0.6 mm<sup>2</sup>.

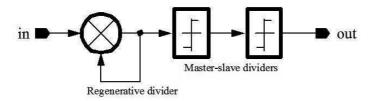

# 2.3. Divide-by-8 Chain

The divide-by-8 chain consists of a regenerative divider followed by two master-slave dividers as shown in Figure 7. The output of each stage should be able to drive the next stage. From the simulation, each stage output is estimated to generate more than 60 mV to enable to drive the next stage.

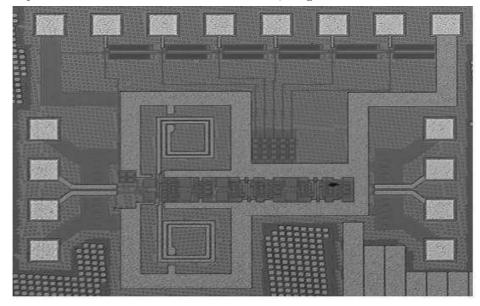

Figure 8 shows the die micrograph of the divide-by-8 chain. The circuit consumes  $0.7 \text{ mm} \times 0.8 \text{ mm}$  area including the pads. This is due to the fact that most of the master-slave divider test circuit is consumed by the test pads. Hence, the combined circuit resulted in a small area that is mainly dominated by the regenerative divider.

Figure 7. Divide-by-8 chain. This chain consists of three dividers, a regenerative divider and two master-slave dividers.

Figure 8. Die micrograph of the divide-by-8 chain in 0.18  $\mu m$  SiGe BiCMOS technology. The circuit area is 0.7  $\times$  0.8 mm<sup>2</sup>.

# 3. EXPERIMENTAL RESULT

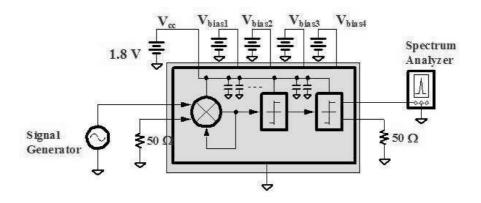

The circuits are tested by a pico-second probe with a single-ended input signal. Figure 9 shows the testing configuration for the divide-by-8 chain. External bias voltages are used for optimum circuit operation.

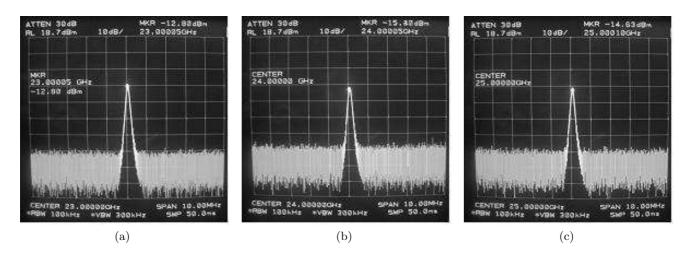

The regenerative frequency divider consumes only 18 mW from 1.8 V supply including the buffer. This circuit is tested using 40 GHz to 50 GHz input range. Figure 10 shows the output spectrum of the divider circuit for three different input frequencies, 46 GHz, 48 GHz and 50 GHz. The output frequency reading is shown on the middle left of each sub-figure, as 23 GHz, 24 GHz and 25 GHz, respectively. Table 1 gives the comparison between input frequency, power consumption and chip area of recently reported regenerative frequency divider.

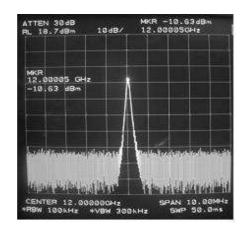

For the master-slave divider, with 1.8 V supply, it consumes 54 mW including the buffer. The maximum operation frequency is 30 GHz. Figure 11 shows the output spectrum at 24 GHz input frequency. Table 2 gives the comparison between input frequency, power consumption, supply voltage and chip area of recently reported static frequency divider in SiGe.

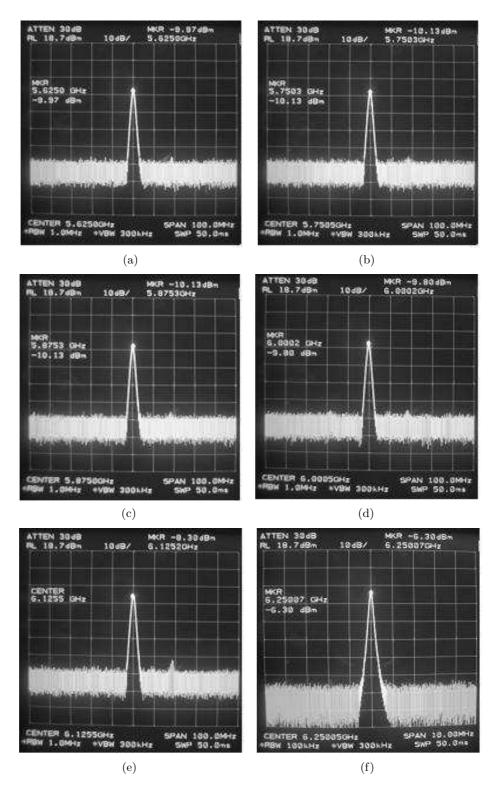

For the divide-by-8 chain, it drains 65 mA from 1.8 V supply voltage. The circuit is tested from 40 GHz to 50 GHz input frequency with 1 GHz frequency steps. Figure 12 shows the output spectrum at six different input frequencies, 45 GHz, 46 GHz, 47 GHz, 48 GHz, 49 GHz and 50 GHz. The output frequency reading is shown on the middle left of each sub-figure, as 5.625 GHz, 5.75 GHz, 5.875 GHz, 6 GHz, 6.125 GHz, and 6.25 GHz, respectively.

Figure 9. Single-ended input test configuration.

Figure 10. Output spectrum for regenerative frequency divider at (a) 46 GHz, (b) 48 GHz, (c) 50 GHz input frequency.

Figure 11. Output spectrum for master-slave frequency divider at 24 GHz input frequency.

Figure 12. Output spectrum for divide-by-8 frequency divider at (a) 45 GHz, (b) 46 GHz, (c) 47 GHz, (d) 48 GHz, (e) 49 GHz, (f) 50 GHz input frequency.

Table 1. Comparison between input frequency, power consumption, and chip area for various regenerative dividers.

| Ref       | Technology                | Frequency (GHz) | Power (mW) | Area including pads (mm <sup>2</sup> ) |

|-----------|---------------------------|-----------------|------------|----------------------------------------|

| 4         | $0.25~\mu\mathrm{m}$ SiGe | 103             | 195        | 0.50                                   |

| 6         | $0.15~\mu\mathrm{m}$ SiGe | 110             | 310        | 0.25                                   |

| 7         | $\operatorname{SiGe}$     | 63              | 470        | 0.81                                   |

| 8         | $0.15~\mu\mathrm{m}$ GaAs | 28              | 100        | 4.50                                   |

| This work | $0.18~\mu\mathrm{m}$ SiGe | 48              | 18         | 0.42                                   |

**Table 2.** Comparison between input frequency, power consumption, supply voltage, and chip area for various static dividers in SiGe.

| Ref       | Technology                | Frequency (GHz) | Power (mW) | Supply voltage (V) | Area including pads (mm <sup>2</sup> ) |

|-----------|---------------------------|-----------------|------------|--------------------|----------------------------------------|

| 4         | $0.25~\mu\mathrm{m}$ SiGe | 71              | 140        | 3.5                | 0.50                                   |

| 9         | $0.18~\mu\mathrm{m}$ SiGe | 42              | 160        | 2.1                | 0.28                                   |

| 10        | $0.35~\mu\mathrm{m}$ SiGe | 71.8            | 594        | 4.5                | 0.25                                   |

| This work | $0.18~\mu\mathrm{m}$ SiGe | 30              | 54         | 1.8                | 0.36                                   |

#### 4. CONCLUSION

Three types of dividers fabricated in 0.18  $\mu m$  SiGe BiCMOS technology are reported. The dividers are part of a frequency synthesizer for a 60 GHz receiver. The dynamic divider employs a regenerative structure. The regenerative divider handles very high frequencies, up to 50 GHz and consumes 18 mW from 1.8 V supply voltage. Meanwhile, the static divider employs a conventional master-slave structure. The master-slave divider operates up to a 30 GHz input frequency from a very low supply voltage, 1.8 V. In addition, a divide-by-8 chain, which is a combination of a regenerative and two master-slave dividers has been presented.

# REFERENCES

- 1. A. Q. Safarian and P. Heydari, "Design and analysis of a distributed regenerative frequency divider using distributed mixer," in *International Symposium on Circuits and Systems*, pp. 992–995, (Vancouver, Canada), 2004.

- 2. R. Harrison, "Theory of regenerative frequency dividers using double-balanced mixer," in *IEEE Microwave Theory and Techniques Society (MTT-S) Digest*, pp. 459–462, (Long Beach, USA), 1989.

- 3. C. Rauscher, "Regenerative frequency division with a gaas fet," in *IEEE Microwave Theory and Techniques* (MTT), vol. 32, pp. 1461–1468, 1984.

- 4. L. Wang, Y. M. Sun, J. Borngraeber, A. Thiede, and R. Kraemer, "Low power frequency dividers in SiGe:C BiCMOS technology," in *Proc. Silicon Monolithic Integrated Circuits in RF Systems (SiRFIC)*, pp. 357–360, (Greece), 2006.

- 5. A. Rylyakov, "A 51 GHz master-slave latch and static frequency divider in 0.18  $\mu$ m SiGe BiCMOS," in *IEEE Bipolar/BiCMOS Circuit and Technology Meeting (BCTM)*, pp. 75–77, (Toulouse, France), 2003.

- 6. H. Knapp, M. Wurzer, T. F. Meister, K. Aufinger, J. Bock, S. Boguth, and H. Schafer, "86 GHz static and 110 GHz dynamic frequency dividers in SiGe bipolar technology," in *IEEE Microwave Theory and Techniques Society (MTT-S) Digest*, pp. 1067–1070, (Philadelphia), 2003.

- 7. J. Mullrich, W. Klein, R. Khlifi, and H. M. Rein, "SiGe regenerative frequency divider operating up to 63 GHz," in *Electronic Letters*, vol. 35, pp. 1730–1731, 1999.

- 8. L. Landen, C. Fager, and H. Zirath, "Regenerative GaAs MMIC frequency dividers for 28 and 14 GHz," in *Gallium Arsenide Applications Symposium*, (Paris, France), 2000.

- 9. D. Kucharski and K. T. Kornegay, "A 40 GHz 2.1 V static frequency divider in SiGe using a low-voltage latch topology," in *IEEE Radio Frequency Integrated Circuits Symposium*, pp. 461–464, (Boston), 2005.

- 10. M. Wurzer, J. Bock, H. Knapp, K. Aufinger, and T. Meister, "71.8 GHz static frequency divider in a SiGe bipolar technology," in *IEEE Bipolar/BiCMOS Circuit and Technology Meeting (BCTM)*, pp. 216–219, (Monteray, USA), 2002.