## A Pulse-Frequency Modulation Sensor Using Memristive-Based Inhibitory Interconnections

Omid Kavehei<sup>1</sup>, Sang-Jin Lee<sup>2</sup>, Kyoung-Rok Cho<sup>2,\*</sup>, Said Al-Sarawi<sup>3</sup>, and Derek Abbott<sup>3</sup>

<sup>1</sup> Centre for Neural Engineering, The University of Melbourne, VIC 3010, Australia

<sup>2</sup> School of Electrical and Electronic Engineering, The University of Adelaide, SA 5005, Australia

<sup>3</sup> College of Electrical and Information Engineering, WCU Program, Chungbuk National University, Cheongju, 361-763, Korea

This paper proposes a programmable inhibitory interconnection network between pixels in an array of novel low-voltage Schmitt-trigger-based PFM sensors that will be of interest for future applications in memristor-based early vision processing. In addition, a new low-power inverter-based pulse-frequency modulation (PFM) design and its integration with the network is also presented. To ensure no change in the memristors conductance in the network, the CMOS imager was designed for low voltage operation. That has resulted in a significant power reduction, better than 60%, and a comparable linear dynamic range when compared to published designs in the literature. The design was performed using a 0.13 um Samsung Electronics standard CMOS process, using 0.75 V supply voltage.

**Keywords:** Memristive Devices, CMOS Image Sensor, Pulse-Frequency Modulation.

#### 1. INTRODUCTION

The light intensity can be represented either as pulse-frequency (pulse-frequency modulation (PFM)), pulse-width (pulse-width modulation (PWM)), pulse-amplitude (pulse-amplitude modulation (PAM)), or phase (pulse-phase modulation (PPM)) of a signal. The targeted application for the proposed sensor is an early vision processing system using a CMOS image sensor that uses a memristor-based crossbar array combined with either a PWM or PFM sensors. According to Figures 2 and 7 in Ref. [16], PWM and PFM sensors can be used for building a vision chip in combination with a resistive network. With the emergence of new nanostructure and nano-devices and the possibility of integrating some of these devices with main stream CMOS technologies, new approaches for circuits and systems are possible.

One of these emerging devices is the memristor, which was postulated by Leon Chua in 1971 as the fourth fundamental circuit element, that links magnetic flux to electric charge.<sup>5</sup> This device was later demonstrated by HP at nanometer scale level in 2008.<sup>19</sup> The new device has a non-volatile internal state that can be programmed electrically by controlling the voltage across the device and current passing through it overtime resulting in a linear conductance at some parts of its characteristics.<sup>9</sup>

In bio-inspired imager design, shunting inhibition models of biological vision systems are used to provide local and global adaption mechanisms to improve the quality of captured images to perform some early vision processing such as image enhancement and edge detection.<sup>4</sup> In some CMOS-based implementations, a resistive network is used to implement the needed convolution kernels.<sup>13</sup> However, using resistors is both area hungry and suffers from process variation. Another alternative is to use transistors operating in the linear region of operation with their conductance tuned external by controlling the gate-source voltage of these devices.<sup>6</sup>

However, this approach has a number of limitations: (i) the transistors size used is large and its size is dictated by the used fabrication process, (ii) a bias voltage will always be needed to maintain the device operation at a specific conductance, and more importantly (iii) the transistor conductance is not constant as it is a function of the drain-to-source voltage. The later presents an significant issue as interaction between adjacent pixels needs to be constant. Another approach is to use current mode circuit to build these shunt inhibition kernels. However, area requirements are still an issue in addition to associated process variation and needed control signals. In light of these limitations, memristor, as a fundamental element, presents itself as an ideal candidate in terms of small area, linear conductance and programmability. How the signal area, linear conductance and programmability.

<sup>\*</sup>Author to whom correspondence should be addressed.

Also, using the memristor will continue to allow higher degrees of parallel processing capability which is well matched with the early vision information processing in mammalian retina.<sup>7,23,20</sup> It is suggested that memristive devices can be used to implement the outer plexiform layer (OPL) and the horizontal and bipolar cells in the inner plexiform layer (IPL).<sup>7</sup> The photoreceptor layer can either provide a pulse amplitude (PAM), width (PWM), or frequency (PFM) to be compatible with the memristive grid. From a system level design approach, there is a need to design and tested each individual module to ensure an appropriate functionality. For instance, here we proposed a novel PFM circuit which operates at low-voltages close to  $V_{\rm DD}/2$  that allows the circuit to works below the memristor's threshold voltage and, as a result, the memristor's conductance is maintained during the mutual inhibitory process.

This paper is organized as follows. Section 2 discusses the PFM sensor concept, followed by a review of previous works on designing PFM sensors in Section 3. Comparison between the proposed PFM sensor and available sensors in the literature is given in Section 4. Section 5 discusses an application of memristive devices in implementing a programmable inhibitory interconnections between PFM pixels.

In this paper, a memristor (memristive device) is a bipolar Resistive Random Access Memory (ReRAM) that its underlying physics of switching and/or gradual change of resistance can be described based on either Valance Change Memory (VCM) or Electrochemical Metalization (ECM)systems. Each cell contains one diode and one ReRAM device (1D1R). These diodes are special designed diodes (two diodes configurations) that enables a 'bipolar' ReRAM device operates with both positive and negative potential differences.

# 2. PULSE-FREQUENCY MODULATION SENSOR

The core part of the PFM sensor is an oscillator. One of the first oscillators is current-controlled oscillators. Due to a direct relation between frequency and power in these oscillators, a large amount of power will be consumed to produce a high rate frequency and, therefore, they are very attractive for biomedical applications. The conceptual schematic of the PFM digital pixel, which is also known as light-control oscillator (LCO), is shown in Figure 1(a). When the photodiode node (PD) is initially charged to  $V_{\rm DD}$  and then its voltage,  $V_{\rm pd}$ , decreases in proportion to the incident light intensity. Once  $V_{\rm pd}$  reaches a predefined reference voltage level,  $V_{\rm ref}$ , the comparator's output switches from a high voltage (logic "1") to a low voltage (logic "0").

The PWM can be achieved by removing the feedback loop and resetting the photodiode using an external input.

One of the basic differences between the two structures is that there is no initial reset phase in PFM, while in PWM the reset signal is controlled externally so the photodiode can be precharged to  $V_{\rm DD}$ . So, the operation of a PWM structure can be described mathematically as

$$T_d = \frac{(V_{\rm DD} - V_{\rm ref})C_d}{i_d} \tag{1}$$

where  $T_d$  represents the discharge time of the photodiode capacitor,  $C_d$ , node voltage,  $V_{\rm pd}$ , from  $V_{\rm DD}$  to  $V_{\rm ref}$ . The  $i_{\rm dm}$  shows the total current, which is the sum of photo-current,  $i_{ph}$ , and dark current,  $i_d$ . Therefore, the pulse width at the comparator's output can be modulated by the incident light intensity.<sup>3, 10, 14</sup> Therefore, the comparator's output pulls the feedback node (fb) down, so the photodiode is recharged to  $V_{\rm DD}$  through the reset transistor,  $M_{\rm rst}$ . This scheme shows a multiple-reset structure which reduces the photo-current saturation problem and produces a digital pulse frequency as a result of the iterative resetting scheme. Thus, the operation of a PFM structure can be define as

$$f = \frac{i_{\rm pd}}{(V_{\rm DD} - V_{\rm ref})C_{\rm pd}} \tag{2}$$

where f is the output frequency that acts as input clock for a n-bit inpixel counter,  $i_{\rm pd}$  is the sum of photo and dark currents, and  $C_{\rm pd}$  is the photodiode parasitic capacitance. There are several advantages in using a PFM pixel. Firstly, the digital output is far more robust compared to its analogue counterpart in terms of the overall noise effects.

Secondly, it is far less sensitive to the supply voltage scaling since the optical energy is directly converted into a floating-point like digital frequency, so the pixel's performance constraints are no longer dependent on the output voltage dynamic range. This advantage significantly helps to increases frequency dynamic range and linearity of the conversion process.<sup>22</sup> These advantages motivate us to design a new PFM pixel that consumes less power and operates under a relatively low supply voltages to study the inhibitory interconnections between cells.

In the literature, various approaches for designing a PFM image sensor are investigated.<sup>8,17,22</sup> In this paper, we propose a new design for an inverter-based PFM (iPFM), which consumes less power and has a comparable dynamic range with conventional implementations. To obtain this efficient PFM, various Schmitt-trigger gates were used and their effect on the main signal path, power consumption, and the dynamic range were investigated. Simulation results show that, the proposed design, which uses a non-symmetric Schmitt trigger,<sup>1</sup> result in a low-voltage PFM that can operate from a low supply voltage (0.75 V) and provides low-power consumption, while retaining a comparable dynamic range of operation with the conventional Schmitt trigger, inverter-based, or operational transconductance-amplifier-based designs.

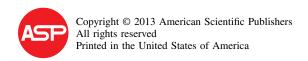

Fig. 1. Pulse-frequency modulation pixels. (a) A generic implementation, indicating the feedback and the main path branches. The yellow box illustrates the feedback inverter chain. If the **X** signal is shown in green in (c)–(f) the signal passes three inverters and if it is red the signal passes only two inverters. Voltage control,  $V_{\text{CTRL}}$ , is applied to control the speed of feedback. (b) An inverter-based pixel with all inverters in the main path (pix-conv1). <sup>10</sup> (c) Schmitt-trigger circuit for replacing the comparator in (a). This is a conventional implementation of a Schmitt-trigger circuit (pix-conv2). (d) A single inverter implementation of the main path (pix1). (e) (from Ref. [1]) and (f) (from Ref. [24]) show two types of low power Schmitt-trigger circuits to be used as a replacement for the first inverter. The designs are called pix2 and pix3 in simulations and experiments. This is the first try to combine the pix2 circuit in (e) with a PFM pixel implementation. A  $10 \times 10 \ \mu\text{m}^2$  layout of the PFM pixel based on (e) is also shown.

### 3. PREVIOUS WORK ON PFM SENSORS

Several parameters should be considered when selecting a comparator these includes, input referred offset voltage, gain variation, area, switching delay, minimum and maximum detectable illuminations, low-voltage operation, etc. An experimental study, in Ref. [22], shows a two-stage comparator and a symmetric operational transconductance amplifier (OTA)-based designs. The switching delay of this comparator is dependent on the voltage difference at the input, while switching delay in the Schmitt trigger is constant due to the inherent positive feedback in these structures. However, this results in a lower frame rate.<sup>22</sup> An increase in the integration time is a problematic as this will result in modifying the memristor's conductance.

In order to design a new low power PFM, previous designs could be examined and also some new designs that are not considered in previous studies. Firstly, a design that is shown Figure 1(b) and is named "pix-conv1" in simulations. <sup>10</sup> This design uses conventional inverters that are placed in the main signal path. The first two inverters in this chain are for discharging the photodiode and the last one is to reset the photodiode and start a new pulse. The other inverter that is out of the chain is just a signal

shaping inverter. This design can be modified if the PMOS reset transistor is replaced with a NMOS transistor. This replacement helps having lower power consumption due to removing the short circuit current when NMOS is on at the cost of using more silicon area. In addition, this change results in a better FPN in terms of threshold voltage,  $V_{\rm th}$ , variation of the MOSFET devices.3,22 Note that a significant amount of consumed power is dissipated by the first inverter. Therefore, to reduce this power the first inverter can be replaced with a hysteresis adjustable conventional Schmitt trigger gate as shown in Figure 1(c). In this figure, only the main path is shown and the photodiode, reset transistor, and the feedback path are omitted to highlight the new changes to the circuits. This design is named "pix-conv2." Based on our simulations, in order to have a dynamic range similar to previous published designs, the supply voltage should be 0.9 V and because of the power hungry Schmitt trigger this design consumes higher power. Furthermore, the standard deviation of power consumption in this design is relatively high, as shown in Figure 1, implying a highly unpredictable power performance.

One idea that results in lower power consumption is inserting a CMOS inverter between nodes  $V_{\rm PD}$  and  ${\bf X}$ , as in Figure 1(d) as "pix1." The other inverter is the output inverter. This design is also simulated and the results are reported for the comparison, in Figures 2 and 3. Depending on the number of inverters in the main signal path, even or odd number, the output of the main signal path should be connected to an appropriate number of inverters in the feedback. To further reduce the power, the simple inverter was replaced with a low power Schmitt trigger in Figure 1(e) which is previously presented in Ref. [1]. In addition, another Schmitt trigger design for designing a low power PFM is shown Figure 1(f).<sup>24</sup> The longed for this paper design expectation implies that choosing a CMOS inverter will be a good approach. The inverter-based PFM (iPFM)

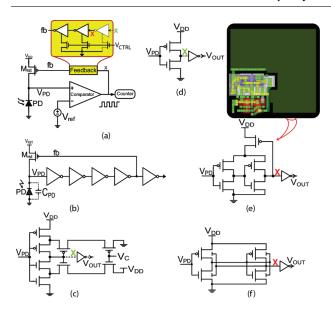

**Fig. 2.** Power dissipation of the PFM pixels in Figure 1 under a wide range of light intensities. It is clear that the pix2 (Fig. 1(e)) and pix3 (Fig. 1(f)) are far more improved than the other circuits in terms of both mean power dissipation and also predictability of power dissipation under a wide range of light intensities. The pix2 shows the lowest and the pix-conv2 demonstrates the highest deviation from their mean power consumption.

structure present a promising option for low-voltage operation and low-power applications such as implantable devices and mobile applications.<sup>22, 10</sup> A few types of iPFM pixels have been introduced in Refs. [10, 21] but despite all of these advantages, all of them suffer from: (i) a considerable increase in power consumption, and (ii) the the feedback inverters were placed in the main signal path. The design named pix2 (Fig. 1(e)) shows a better power consumption in terms of variation and mean value, as demonstrated in Figure 1. Figures 1(d) and (e) illustrate the application of one single inverter and a low power Schmitt-trigger circuit in the design of a PFM pixel.

#### 4. COMPARISONS OF THE PFM PIXELS

The proposed cell was simulated using 130 nm mixed-signal CMOS technology. The supply voltage used for analysing the design is 0.75 V, while the nominal  $V_{\rm DD}$  of the process is 1.2 V. The feedback inverter chain is also operating from 0.75 V supply voltage. The control transistor is shared between the three feedback inverters and is controlled using  $V_{\rm CTRL} = 0.6 \times V_{\rm DD}$  (in Fig. 1(a)), while the reset supply voltage has been set to about the same value. Thus, the control signal can be directly connected to the reset supply voltage. Implemented layout that is shown in Figure 1(e) demonstrates a fill factor of 65%.

A comparison between these cells is shown in Figure 2. A post-layout Cadence simulation at 0.75 V shows better than 60% reduction in the mean value of total power consumption for the proposed structure while the dynamic range and the frequency response linearity are still comparable with the conventional design, as illustrated in Figure 3. Figure 2 shows the proposed circuit consumes 60% less power compare to "pix1," which has closest power consumption to the proposed structure "pix2." We have calculated this improvement using mean values of power. Low photo currents range are not shown in Figure 3. The simulations have been carried out using

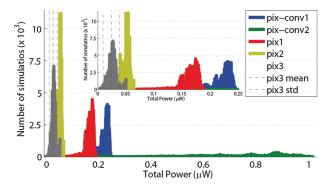

**Fig. 3.** Dynamic range of the PFM pixels within the range of 1pA to 10nA photocurrent (plus dark current). Clearly, the ratio of the low and high frequencies for all the circuits indicate very close results in terms of dynamic range. Therefore, the pix2 can be considered as a design that provides comparable dynamic range with lower power consumption.

different light intensities. Low frequencies can be measured (from the actual fabrication) down to a few Hz but a linear frequency response corresponding to the log-scale light intensity (mW  $\cdot$  cm<sup>-2</sup>) starts around 100 Hz. Therefore, early results show a minimum (detectable intensity) and maximum (maximum intensity) frequencies of  $f_{\rm min} = 100$  Hz and  $f_{\rm max} = 50$  MHz, respectively.

The simulations, however, only carried out in the range of 1 pA to 10 nA to get detectable frequency response from all the circuits. Moving towards high light intensities causes a large nonlinearity at the output pulse-width which should ideally keep a constant value. This nonlinearity then causes a significant degradation in dynamic range as shown in Figure 3. The figure shows the maximum detectable current for both of the designs is to be around 6.7 nA, which corresponds to 60 MHz for the pix2. Clearly, the ratio of the low and high frequencies for all the circuits indicate very close results in terms of dynamic range. Therefore, the pix2 is a design that provides a comparable dynamic range with lower power consumption. The pix3, Figure 1(f), however, shows a better overall performance in Figures 2 and 3. The main reason that the pix3 is not a good option is because of its layout complexity. Connecting body contacts of the MOSFET transistors to any other voltages than the lowest and highest potentials creates a significant complexity in terms of layout implementation and increased pixel area to meet the design rules for wells biased at different voltages.

#### 5. INHIBITORY INTERCONNECTIONS

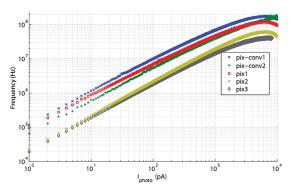

An inhibitory interconnection can be realised in a PFM image sensor with a simple addition of a reset transistor (Fig. 4(b)), in this case the reset in the pixel controlled by the neighbouring cells and not the pixel's output.<sup>16</sup> This interconnection can be implemented in a flexible fashion by utilising the capabilities of the nonvolatile, programmable, and small area memristive device.

In addition to the programmability and non-volatility of memristors, they are capable of storing multilevel intermediate states. For instance, recently, it has experimentally observed that a memristor is capable of storing up to tens of different states. 12,2 This adaptivity can be utilized to serve different purposes in early vision processing. In this paper we have adapted a memristor model in Ref. [11]. The model suggests that the highly nonlinear switching dynamics of the memristor is perhaps due to thermal effects, which implies a switching speed in the range of nanoseconds whena larger voltage than the memristor's threshold voltage is applied. This threshold voltage is around 2.0 V, which is much higher than the image sensor's operational voltage of 0.75 V. Therefore, we neither expect switching nor any change in the memristor's state variable (conductance). Figure 4(a) shows the configuration of pixels that consist of Figure 1(e) and memristive device

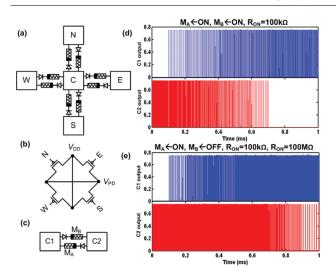

**Fig. 4.** Mutual inhibitory interconnection in a memristive device based PFM network. (a) The interconnection network as seen by the cell C. The cell C (Center) is connected to E (East), W (West), N (North), S (South) through a memristive device. The diode acts as a selective device to reduce parasitic currents in a crossbar network. (b) The transistors required to connect one cell (C) to four of the surrounding cells (E, W, N, S).  $V_{\rm PD}$  is the photodiode node in Figure 1(e) Two pixels are connected using two memristive devices and simulations results are illustrated in (d) and (e). (d) Memristor A and B are ON.  $R_{\rm ON} = 100~{\rm k}\Omega$ . (e) Memristor A is ON and Memristor B is OFF.  $R_{\rm OFF} = 100~{\rm M}\Omega$ .

interconnections. Each pixel contains a network of PMOS reset transistors that is connected in parallel with its internal reset transistor between the supply node  $V_{\rm DD}$  and the photodiode node  $V_{\rm pd}$ . Connections between either E, W, N, or S cells and C are between node X in Figure 1(e) and E, W, N, or S PMOS's gates in Figure 4(b). For simulations, two cells, C1 and C2, are connected together using two memristive devices,  $M_A$  and  $M_B$ , that are initially programmed as ON with an  $R_{\rm ON} = 100 \text{ k}\Omega$ . Cell C2 responds to a range of incident lights ranging from high to low, corresponding to high frequency and low frequency outputs, respectively. While cell C1 responds to a constant light intensity equal to the average light intensity for cell C2. Simulation allows 1 ms time to collect responses. Normally, during the simulation time, C1's output should result in a constant pulse-frequency, while C2 output varies from a high pulse-frequency to a low pulse-frequency compare to the C1 output. However, because of the given setup and mutual inhibitory interconnections, both outputs should suppressed each other. This is clearly demonstrated in Figure 4(d), where both memristors are ON.

It is observed that like conventional inhibitory interconnections, firing rates in the two cells suppress each other. When C2 firing rate is high, C1 firing rate is suppressed and consequently when C2 firing rate is low, it is output rate is suppressed. To show the flexibility of our approach, we programmed Memristor B on its OFF state,  $R_{\rm OFF} = 100~{\rm M}\Omega$  (Fig. 4(e)). This allows the firing rate of C2 to suppress firing rate of C1 (through Memristor A), the connection between C2 and C1 can be seen as an open circuit.

Different resistance level programming can therefore result in different mutual inhibitory scenarios. Design of such network requires an extensive analysis of time constant due to the inherent parasitic gate capacitance of PMOS transistor and memristive device's resistance, which set the response time of the transistor in order to suppress firing rate of adjunct cells. In the current approach the memristor's state must stay unchanged. Therefore, utilising a low voltage PFM sensor is important and prevent programming the memristor during operation.

#### 6. CONCLUSION

This paper proposes a programmable inhibitory interconnection network between an array of novel low-voltage Schmitt-trigger-based PFM sensor. The low power Schmitt-trigger circuits helped in reducing the supply voltage requirements down to 0.75 V and at the same time retain the output signal characteristics, such as a constant pulse width, and also dynamic range of the response. The total power dissipation reduced by around 60% and the standard deviation of power consumption is also significantly improved.

The inhibitory interconnections in the proposed sensor uses of a new nanodevice named memristor, which promises a new generation of applications that are not possible using standard bulk CMOS technology. The memristor can be integrated with current CMOS technology. The characteristics of the memristor-based inhibitory interconnections was verified through simulations using an experimentally verified memristor model.

**Acknowledgment:** Image sensor fabrication in this work was supported by IDEC and the World Class University (WCU) project of MEST and KOSEF through CBNU under grant No. R33-2008-000-1040-0 and the School of Electrical and Electronic Engineering of Adelaide University, through the Simon Rockliff Scholarship and an early career research grant from Melbourne School of Engineering, The University of Melbourne. This work (2011 0015702) was supported by Mid-career Researcher Program through NRF grant funded by the MEST.

### **References and Notes**

- 1. S. F. Al-Sarawi, Electron. Lett. 38, 1009 (2002).

- F. Alibart, L. Gao, B. D. Hoskins, and D. B. Strukov, Nanotechnology 23, 075201 (2012).

- A. Bermak, A. Bouzerdoum, and K. Eshraghian, *Microelectron. J.* 33, 1091 (2002).

- 4. F. Boussaid, A. Bermak, and A. Bouzerdoum, A wide dynamic range CMOS imager with extended shunting inhibition image processing capabilities, *IEEE International Symposium on Circuits and Systems*, *ISCAS* (2001), pp. 620–623.

- 5. L. O. Chua, IEEE Transactions on Circuit Theory 18, 507 (1971).

- J. Fernández-Berni and R. Carmona-Galán, International Journal of Circuit Theory and Applications (2011).

- A. Gelencser, T. Prodromakis, C. Toumazou, and T. Roska, A Biomimetic Model of the Outer Plexiform Layer by Incorporating Memristive Devices, npre.2011.6664.1 (2011).

- 8. S. Hinckley, P. V. Jansz, E. A. Gluszak, and K. Eshraghian, Modelling of device structure effects on electrical crosstalk in back illuminated CMOS compatible photodiodes, *Conference on Optoelectronic and Microelectronic Materials and Devices* (2002), pp. 397–400.

- M. Hu, H. Li, Y. Chen, and X. Wang, Journal of Low Power Electronics 7, 234 (2011).

- K. Kagawa, N. Yoshida, T. Tokuda, J. Ohta, and M. Nunoshita, Optical Review 11, 176 (2004).

- 11. O. Kavehei, S. Al-Sarawi, K-.R. Cho, K. Eshraghian, and D. Abbott, *IEEE Transactions on Nanotechnology* 11, 374 (2012).

- K.-H. Kim, S. Gaba, D. Wheeler, J.-M. Cruz-Albrecht, T. Hussain, N. Srinivasa, and W. Lu, *Nano Lett.* 12, 389 (2012).

- 13. H. Kobayashi, J. L. White, and A. A. Abidi, *IEEE Journal of Solid-State Circuits* 26, 738 (1991).

- 14. S. Koppa, Y. Joo, M. Venkataramasubramani, and L. Tang, Nanoscale biosensor chip, 53rd IEEE International Midwest Symposium on Circuits and Systems, MWSCAS (2010), pp. 268–271.

- C. D. Nilson, R. B. Darling, and R. B. Pinter, *IEEE Journal of Solid-State Circuits* 29, 1291 (1994).

- 16. J. Ohta, A. Uehara, T. Tokuda, and M. Nunoshita, Pulse-modulated vision chips with versatile-interconnected pixels, Parallel and Distributed Processing in Lecture Notes in Computer Science, edited by G. Goos, J. Hartmanis, and J. van Leeuwen (2000), pp. 1063–1071.

- D. Park, Y. Joo, and S. Koppa, A simple and robust self-reset CMOS image sensor, 53rd IEEE International Midwest Symposium on Circuits and Systems, MWSCAS (2010), pp. 680–683.

- 18. T. Prodromakis and C. Toumazou, A review on memristive devices and applications, 17th IEEE International Conference on Electronics, Circuits, and Systems (ICECS) (2010), pp. 934–937.

- D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, Nature 453, 80 (2008).

- A. Swaroop, D. Kim, and D. Forrest, Nature Reviews Neuroscience 11, 563 (2010).

- A. Uehara, K. Kagawa, T. Tokuda, J. Ohta, and M. Nunoshita, *Electronics Lett.* 39, 1102 (2003).

- X. Wang, W. Wong, and R. Hornsey, *IEEE Transactions on Electron Devices* 53, 2988 (2006).

- 23. H. Wassle, Nature Reviews Neuroscience 5, 747 (2004).

- C. Zhang, A. Srivastava, and P. K. Ajmera, *Electronics Lett.* 39, 1696 (2003).

Received: 7 November 2011. Accepted: 12 April 2012.